# **Precision Current Preamplifier**

## **SIM918**

#### Certification

Stanford Research Systems certifies that this product met its published specifications at the time of shipment.

### Warranty

This Stanford Research Systems product is warranted against defects in materials and workmanship for a period of one (1) year from the date of shipment.

#### Service

For warranty service or repair, this product must be returned to a Stanford Research Systems authorized service facility. Contact Stanford Research Systems or an authorized representative before returning this product for repair.

Information in this document is subject to change without notice.

Copyright © Stanford Research Systems, Inc., 2017. All rights reserved.

Stanford Research Systems, Inc. 1290–D Reamwood Avenue Sunnyvale, CA 94089 USA

Phone: (408) 744-9040 • Fax: (408) 744-9049

www.thinkSRS.com • e-mail: info@thinkSRS.com

Printed in U.S.A.

Document number 9-01592-903

## Contents

| Ge | enera                              | l Information                       | iii    |  |  |  |

|----|------------------------------------|-------------------------------------|--------|--|--|--|

|    | Safety and Preparation for Use iii |                                     |        |  |  |  |

|    |                                    | abols                               |        |  |  |  |

|    | Not                                | ation                               | . vii  |  |  |  |

|    | Spec                               | cifications                         | . vii  |  |  |  |

| 1  | Get                                | ting Started                        | 1-1    |  |  |  |

|    | 1.1                                | Introduction to the Instrument      | . 1-2  |  |  |  |

|    | 1.2                                | Front-Panel Operation               | . 1-5  |  |  |  |

|    | 1.3                                | Connections                         | . 1-8  |  |  |  |

|    | 1.4                                | Power-On                            | . 1-9  |  |  |  |

|    | 1.5                                | Restoring the Default Configuration | . 1-9  |  |  |  |

|    | 1.6                                | SIM Interface                       | 1-10   |  |  |  |

| 2  | Des                                | cription of Operation               | 2-1    |  |  |  |

|    | 2.1                                | About Transimpedance Amplifiers     | . 2-2  |  |  |  |

|    | 2.2                                | Bias and Ground                     |        |  |  |  |

|    | 2.3                                | Output                              | . 2-5  |  |  |  |

|    | 2.4                                | Autozero Trim                       | . 2-5  |  |  |  |

|    | 2.5                                | Phase-Locked Loop                   | . 2-6  |  |  |  |

|    | 2.6                                | Autocalibration                     | . 2-6  |  |  |  |

|    | 2.7                                | Clock Stopping                      | . 2-7  |  |  |  |

|    | 2.8                                | Quiescent Operation                 | . 2-8  |  |  |  |

| 3  | Ren                                | note Operation                      | 3 – 1  |  |  |  |

|    | 3.1                                | Index of Common Commands            | . 3-2  |  |  |  |

|    | 3.2                                | Alphabetic List of Commands         | . 3-4  |  |  |  |

|    | 3.3                                | Introduction                        | . 3-6  |  |  |  |

|    | 3.4                                | Commands                            | . 3-7  |  |  |  |

|    | 3.5                                | Status Model                        | . 3-24 |  |  |  |

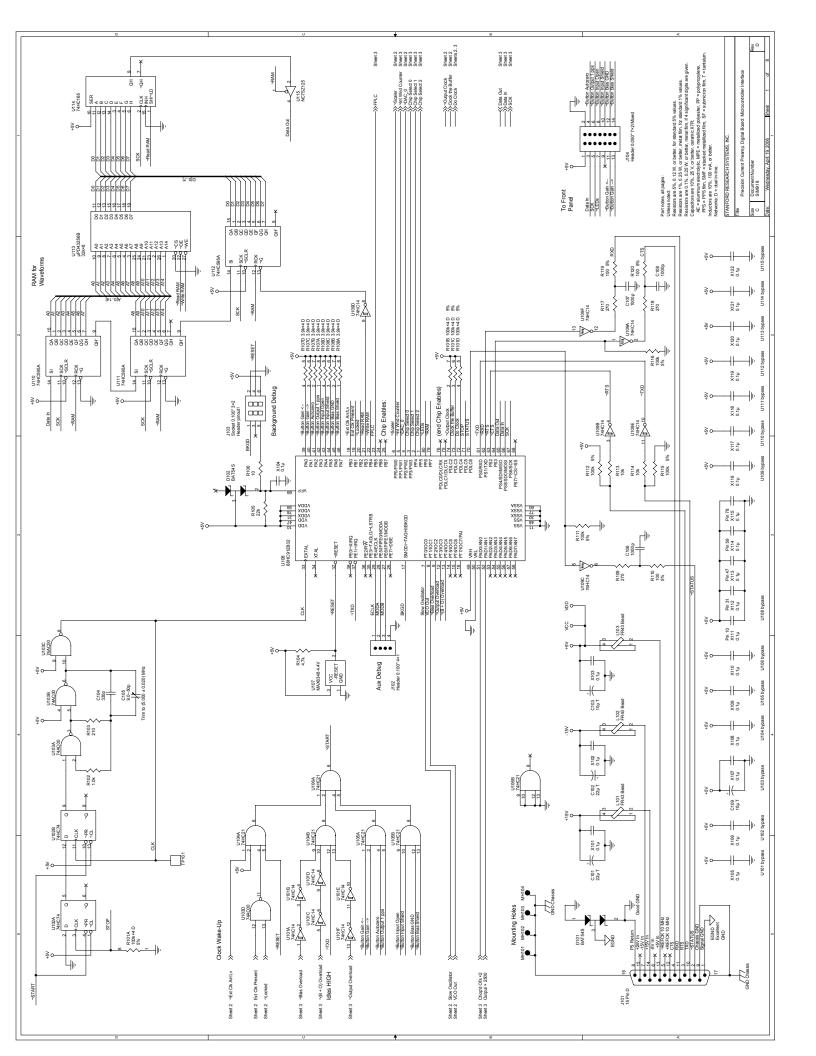

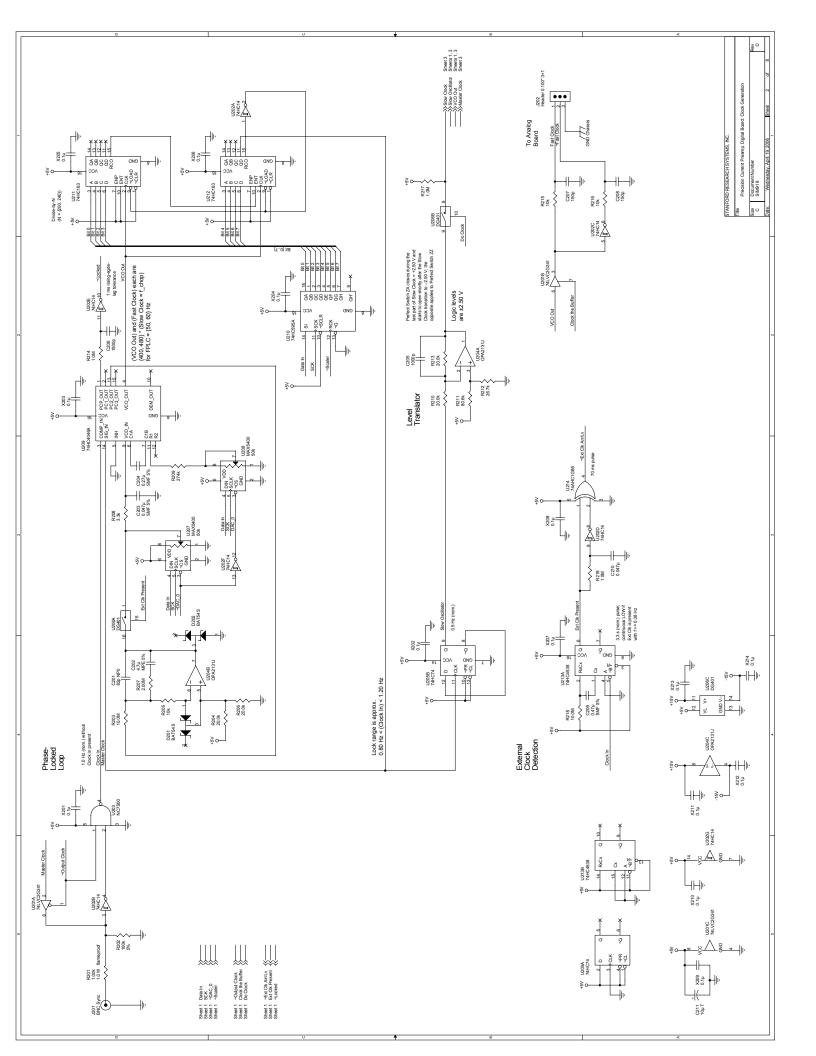

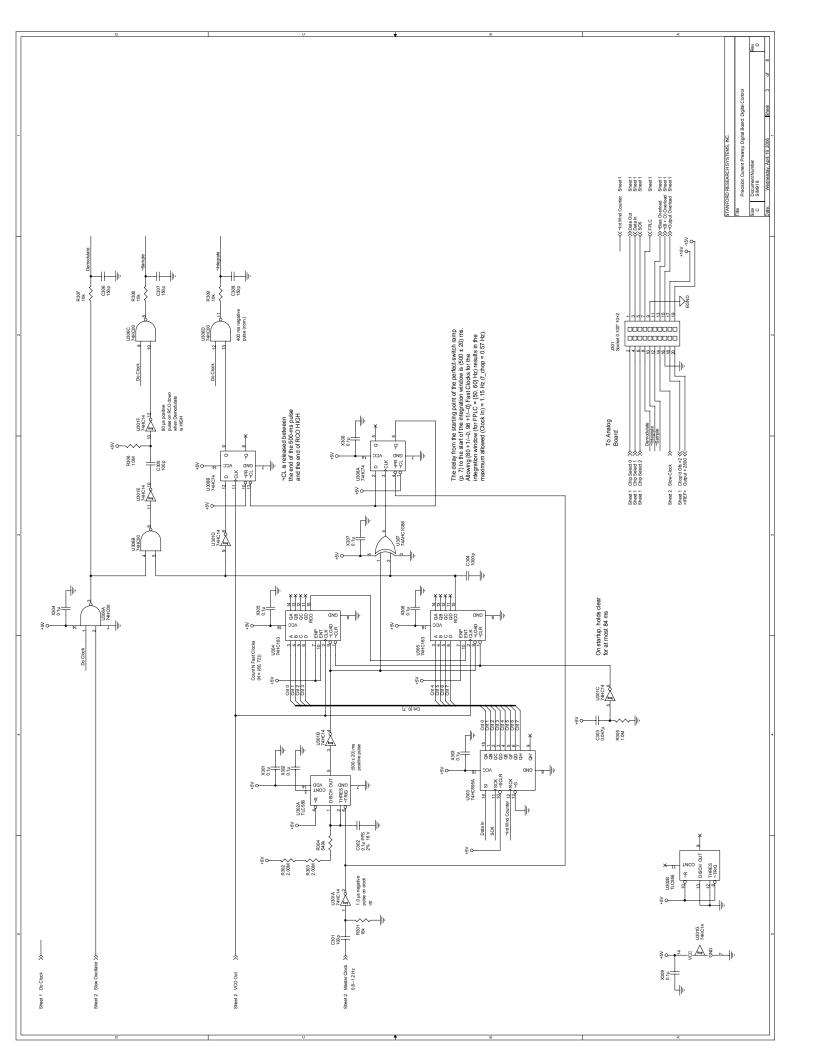

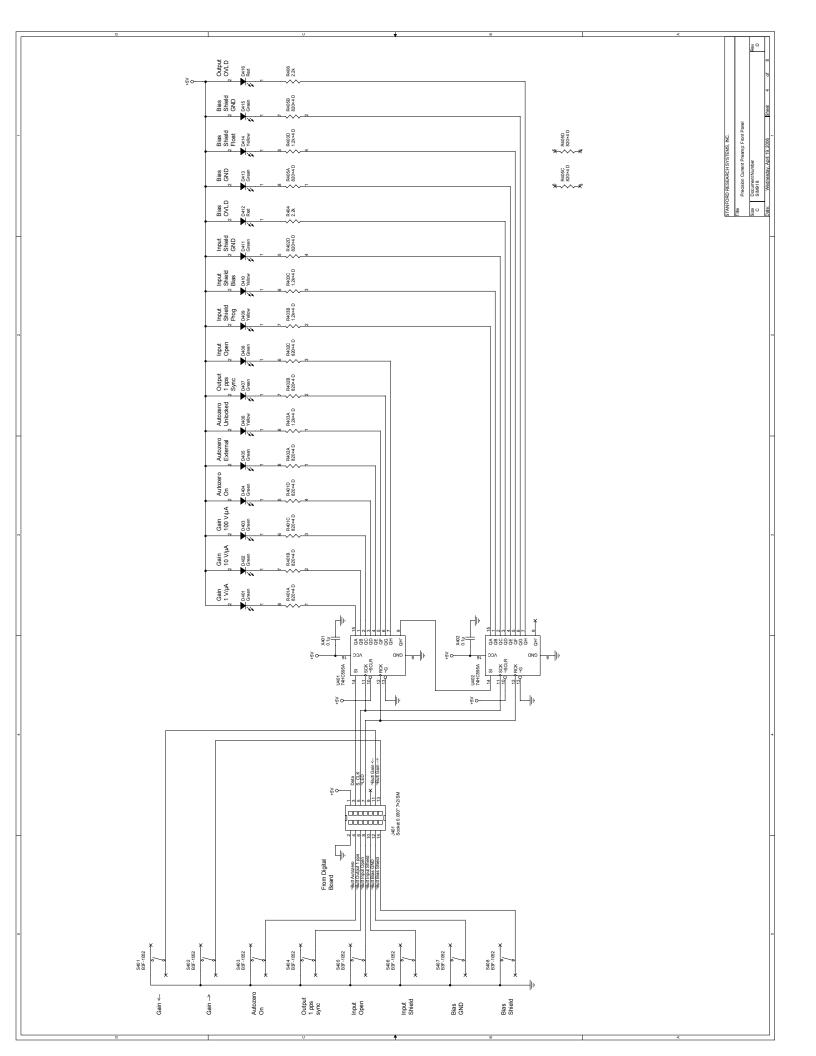

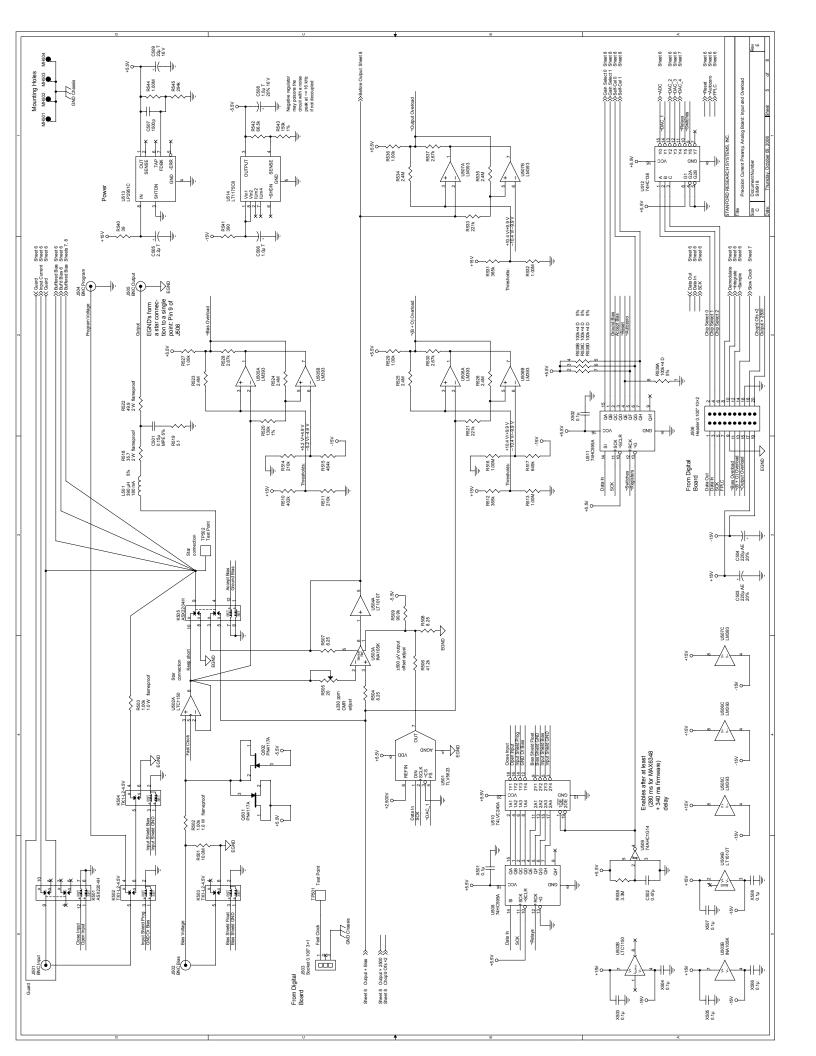

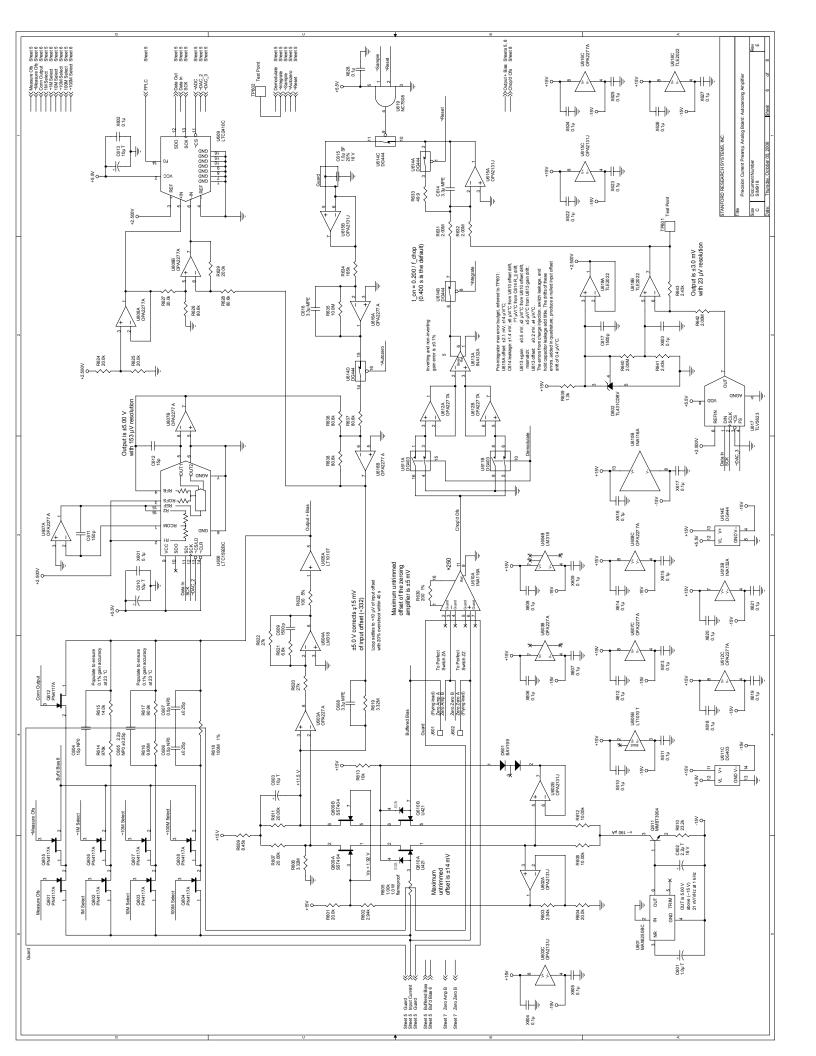

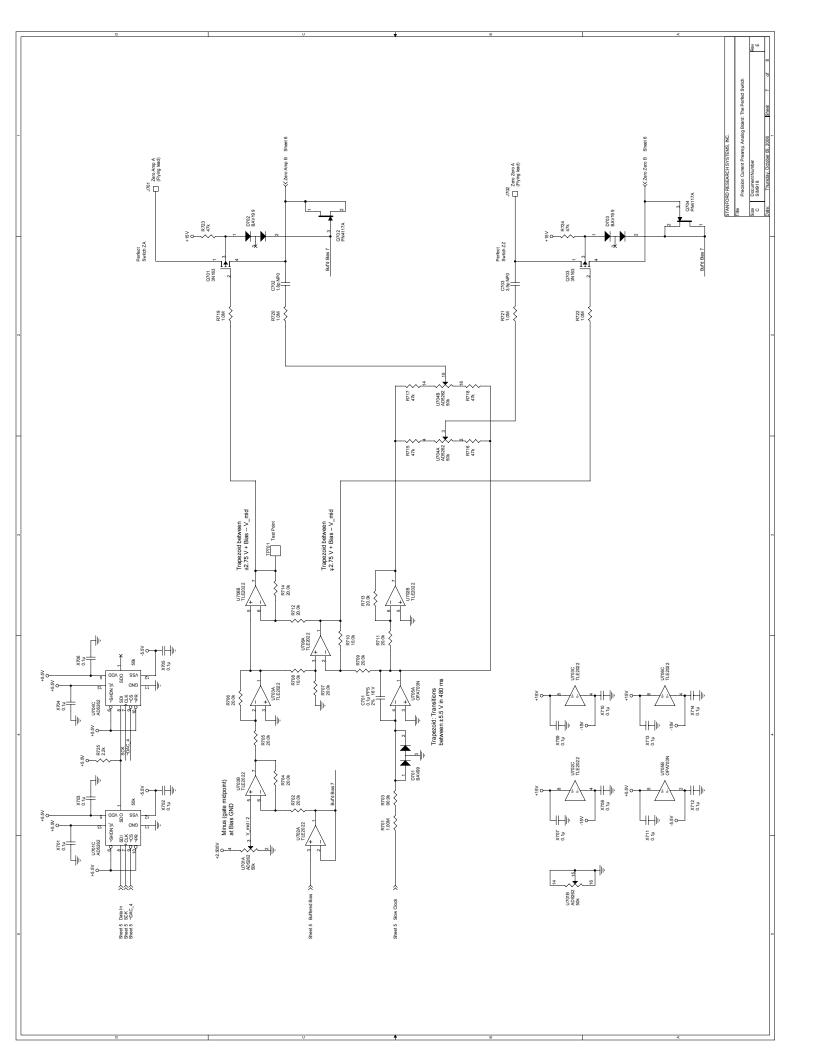

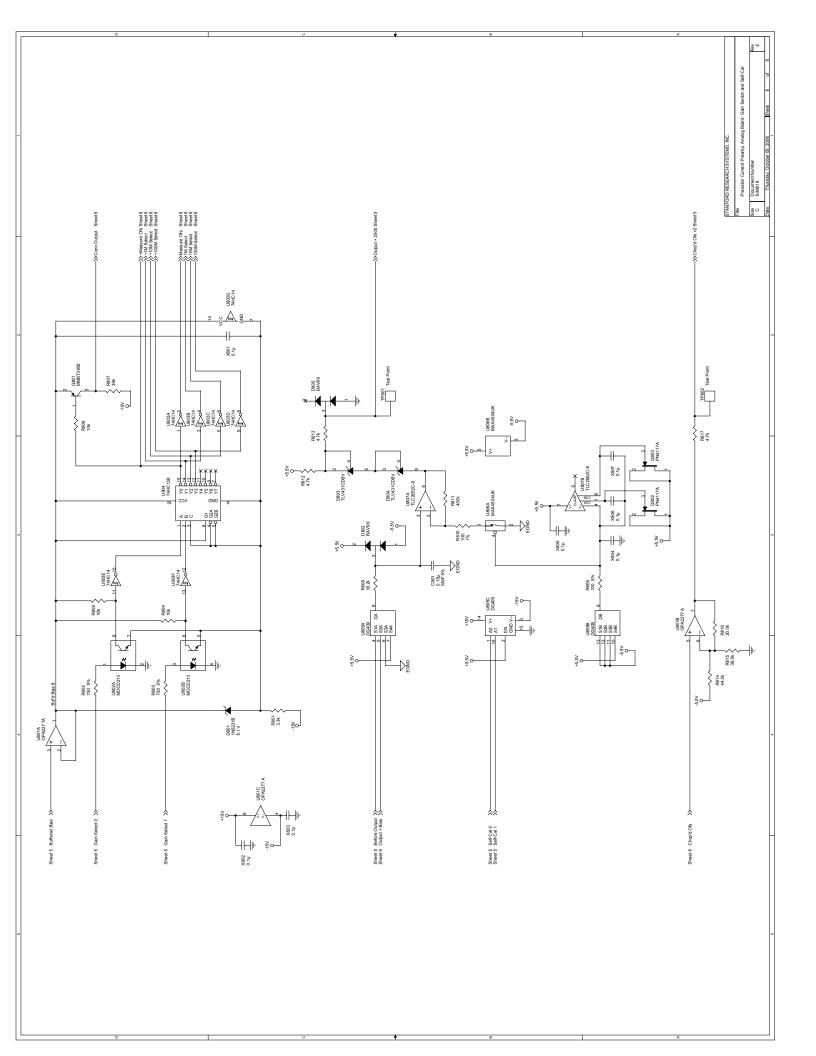

| 4  | Circ                               | cuit Description                    | 4 – 1  |  |  |  |

|    | 4.1                                | Schematic Diagrams                  | . 4-2  |  |  |  |

| A  | Ind                                | ex                                  | A – 1  |  |  |  |

ii Contents

### **General Information**

The SIM918 Precision Current Preamplifier, part of Stanford Research Systems' Small Instrumentation Modules family, converts an input electric current into a proportional voltage output while maintaining zero potential difference between the input terminal and a bias terminal.

The main amplifier stage presents a transimpedance  $R_{\rm F}$ , equal to the current gain of the preamplifier, to an input current  $i_{\rm in}$ . The bias voltage  $V_{\rm bias}$  is subtracted from the output of the stage, so that the voltage at the output of the instrument is

$$V_{\text{out}} = (V_{\text{bias}} - i_{\text{in}} \times R_{\text{F}}) - V_{\text{bias}} = -i_{\text{in}} \times R_{\text{F}}.$$

## Safety and Preparation for Use

#### **Connections**

No dangerous voltages are generated by the module. However, the outer shield of the front-panel Input coaxial (BNC) connector in the SIM918 can be switched to the rear-panel Program input. If a dangerous voltage is applied to the Program terminal, it may be present on the outer shell of the Input connector, and may cause injury or death.

WARNING

Do not exceed  $\pm 60$  volts to the Earth at the center terminal of the rear-panel Shield Program Voltage BNC connector.

Do not exceed  $\pm 15$  volts to the Earth at the center terminal of the front-panel Input and Bias BNC connectors, or at the center terminal of the rear-panel Ref Clock Sync BNC connector.

#### **Biomedical applications**

**MARNING**

Under certain conditions, the SIM918 may prove to be unsafe for applications involving human subjects. Incorrect grounding, component failure, and excessive common-mode input voltages are examples of conditions in which the instrument may expose the subject

iv General Information

to large input currents. Therefore, Stanford Research Systems does not recommend the SIM918 for such applications.

### Caution regarding use with photomultipliers

#### CAUTION

The front-end amplifier of this instrument is easily damaged if a photomultiplier is used improperly with the preamplifier. When left completely unterminated, a cable connected to a PMT can charge to several hundred volts in a relatively short time. If this cable is connected to the curent input of the SIM918, the stored charge may damage the front-end JFET. To avoid this problem, provide a leakage path of about  $100\,\mathrm{k}\Omega$  to ground inside the base of the PMT to prevent charge accumulation.

#### **Service**

Do not install substitute parts or perform unauthorized modifications to this instrument.

### Preparation for use

The SIM918 is a single-wide module designed to be used inside the SIM900 Mainframe. Do not turn on the power to the mainframe or apply voltage or current inputs to the module until the module is completely inserted into the mainframe and locked in place.

General Information v

vi General Information

## Symbols you may Find on SRS Products

| Symbol  | Description                               |  |

|---------|-------------------------------------------|--|

| $\sim$  | Alternating current                       |  |

|         | Caution - risk of electric shock          |  |

| <i></i> | Frame or chassis terminal                 |  |

| A       | Caution - refer to accompanying documents |  |

| Ţ       | Earth (ground) terminal                   |  |

|         | Battery                                   |  |

| $\sim$  | Fuse                                      |  |

|         | On (supply)                               |  |

|         | Off (supply)                              |  |

General Information vii

#### **Notation**

**WARNING**

The following notation will be used throughout this manual:

A warning means that injury or death is possible if the instructions are not obeyed.

**A** CAUTION

A caution means that damage to the instrument or other equipment is possible.

Typesetting conventions used in this manual are:

- Front-panel buttons are set as [GAIN ¬];

[GAIN ¬□] is shorthand for "[GAIN ¬] & [GAIN ¬]".

- Front-panel indicators are set as *OVLD*.

- Signal names are set as ¬STATUS.

- Signal levels are set as HIGH.

- Remote command names are set as \*IDN?.

- Literal text other than command names is set as OFF.

- Special ASCII characters are set as  $\langle CR \rangle$ .

Remote command examples will all be set in monospaced font. In these examples, data sent by the host computer to the SIM918 are set as straight teletype font, while responses received by the host computer from the SIM918 are set as *slanted teletype font*.

viii General Information

## **Specifications**

## **Performance characteristics**

|                      |                                                             | Min  | Тур                                 | Max     | Units    |

|----------------------|-------------------------------------------------------------|------|-------------------------------------|---------|----------|

| Gain                 | Selection                                                   | 10   | $\frac{10^{7}}{6}$ , $10^{7}$ , $1$ | $0^{8}$ | V/A      |

|                      | Accuracy, 10 <sup>6</sup> V/A                               |      | ±0.1                                |         | %        |

|                      | $10^{7} \text{ V/A}$                                        |      | ±0.1                                |         | %        |

|                      | $10^{8}  \text{V/A}$                                        |      | ±2                                  |         | %        |

|                      | Stability, 10 <sup>6</sup> V/A                              |      | ±10                                 |         | ppm/°C   |

|                      | $10^7 \mathrm{V/A}$                                         |      | ±50                                 |         | ppm/°C   |

|                      | $10^8  \text{V/A}$                                          |      | ±100                                |         | ppm/°C   |

| Current input        | Selection                                                   |      | On                                  | , open  |          |

|                      | Offset voltage [1–3]                                        |      |                                     | ±10     | μV       |

|                      | Resistance                                                  |      |                                     | 1       | Ω        |

|                      | Capacitance                                                 |      | 18                                  |         | pF       |

|                      | Bias current, DC [3,4]                                      |      | 1.0                                 | 3.0     | pA       |

|                      | AC [1,4,5]                                                  |      | 3.5                                 |         | pA rms   |

|                      | Current noise at $100 \mathrm{Hz}$ [6], $10^6 \mathrm{V/A}$ |      | 130                                 |         | fA/√Hz   |

|                      | $10^7  \text{V/A}$                                          |      | 42                                  |         | fA/√Hz   |

|                      | $10^{8}  \text{V/A}$                                        |      | 15                                  |         | fA/√Hz   |

|                      | Voltage noise [1,5]                                         |      | 25                                  |         | μV rms   |

|                      | -3 dB bandwidth [6], 10 <sup>6</sup> V/A                    |      | 22                                  |         | kHz      |

|                      | $10^{7}  \text{V/A}$                                        |      | 12                                  |         | kHz      |

|                      | $10^8  \text{V/A}$                                          |      | 4                                   |         | kHz      |

|                      | Terminals                                                   |      |                                     | d BNC   |          |

|                      | BNC shield                                                  | Grou | nd, bias                            | , progr | am /open |

| Bias input           | Selection                                                   |      | On,                                 | ground  | d        |

|                      | Voltage [8]                                                 | -5.0 |                                     | +5.0    | V        |

|                      | Resistance                                                  |      | 10                                  |         | ΜΩ       |

|                      | −3 dB bandwidth                                             |      | 0.2                                 |         | Hz       |

|                      | Terminals                                                   |      | Isolate                             | d BNC   | [7]      |

|                      | BNC shield                                                  |      | Grou                                | nd, flo | at       |

| Program input        | Voltage                                                     | -60  |                                     | +60     | V        |

|                      | Resistance                                                  | 3    |                                     |         | GΩ       |

|                      | Terminals                                                   | Gro  | ounded                              | BNC [   | 9], rear |

| Reference clock sync | Selection                                                   |      | Inpu                                | t, outp | at       |

|                      | Interface                                                   | Re   | ar BNC                              | [9], T  | TL [10]  |

|                      | Input frequency [11]                                        | 0.90 |                                     | 1.10    | Hz       |

|                      | Output frequency                                            |      | 1.0                                 |         | Hz       |

General Information ix

|                        |                           | Min              | Тур      | Max       | Units        |  |

|------------------------|---------------------------|------------------|----------|-----------|--------------|--|

| Autozero               | Selection                 | On, hold         |          |           |              |  |

|                        | Source                    | Interna          | ıl, exte | rnal refe | erence clock |  |

|                        | Switching frequency       |                  | 0.50     |           | Hz           |  |

| Output                 | Voltage [8]               | -10.0            |          | +10.0     | V            |  |

|                        | Maximum current           | ±100             |          |           | mA           |  |

| Short circuit duration |                           |                  | Ir       | definite  |              |  |

| Resistance             |                           |                  | 100      |           | Ω            |  |

| Offset voltage [2      |                           |                  |          | ±50       | μV           |  |

|                        | Common-mode rejection, DC | 80               |          |           | dB           |  |

|                        | Terminals                 | Grounded BNC [7] |          |           | C [7]        |  |

| Operating              | Temperature [12]          | 0                |          | 40        | °C           |  |

|                        | Power                     | -                | +5, ±15  | 5         | V DC         |  |

|                        | Supply current, +5 V      |                  | 100      |           | mA           |  |

|                        | ±15 V                     |                  | 150      |           | mA           |  |

#### Conditions:

- [1] With autozero on.

- [2] Following an autocalibration at  $(23 \pm 5)$  °C within 24 hours.

- [3] 100 s average.

- [4] At 23 °C. Doubles every 6 °C to 10 °C.

- [5] 0.1 Hz to 10 Hz.

- [6] For a 100 pF source capacitance and an infinite source resistance. Higher values of source capacitance or a finite source resistance will degrade these specifications.

- [7] Amphenol 31–10–4052 or similar.

- [8] An overload will be detected and the instrument is not guaranteed to perform properly if these limits are exceeded, or if  $|V_{\text{bias}} i_{\text{in}} \times R_{\text{F}}|$  exceeds the limits. Continuous application of a bias voltage  $V_{\text{bias}}$  in excess of ±15 V will damage the instrument.

- [9] Tyco 227169–4 or similar.

- [10] Rising-edge sensitive.

- [11] External reference clock capture range. The instrument is not guaranteed to perform properly if these limits are exceeded.

- [12] Non-condensing.

#### **General characteristics**

| Interface  | Serial (RS-232) through SIM interface                     |

|------------|-----------------------------------------------------------|

| Connectors | BNC (3 front [7], 2 rear [9]); DB-15 (male) SIM interface |

| Weight     | 1.7 lbs                                                   |

| Dimensions | 1.5" W × 3.6" H × 7.0" D                                  |

X General Information

## 1 Getting Started

This chapter gives you the necessary information to get started quickly with your SIM918 Precision Current Preamplifier.

## In This Chapter

| 1.1 | Introduction to the Instrument |                                 |        |  |

|-----|--------------------------------|---------------------------------|--------|--|

|     | 1.1.1                          | Current amplifiers and autozero | 1 - 2  |  |

|     | 1.1.2                          | Clocks                          | 1 - 2  |  |

|     | 1.1.3                          | Cabling and grounding           | 1 - 3  |  |

|     | 1.1.4                          | Autocalibration                 | 1 - 3  |  |

|     | 1.1.5                          | Remote interface and status     | 1 - 3  |  |

|     | 1.1.6                          | Block diagram                   | 1 - 4  |  |

|     | 1.1.7                          | Front and rear panels           | 1 - 5  |  |

| 1.2 | Front-                         | -Panel Operation                | 1-5    |  |

|     | 1.2.1                          | Gain                            | 1 - 5  |  |

|     | 1.2.2                          | Autozero                        | 1 - 5  |  |

|     | 1.2.3                          | Input                           | 1 - 7  |  |

|     | 1.2.4                          | Bias                            | 1 - 7  |  |

|     | 1.2.5                          | Output overload                 | 1 - 8  |  |

| 1.3 | Conn                           | ections                         | 1-8    |  |

| 1.4 | Power                          | r-On                            | 1-9    |  |

| 1.5 | Resto                          | ring the Default Configuration  | 1-9    |  |

| 1.6 | SIM I                          | nterface                        | 1-10   |  |

|     | 1.6.1                          | SIM interface connector         | 1 - 10 |  |

|     | 1.6.2                          | Direct interfacing              | 1 - 10 |  |

1 – 2 Getting Started

#### 1.1 Introduction to the Instrument

## 1.1.1 Current amplifiers and autozero

A current, or transimpedance, amplifier converts electric current into a proportional output voltage. Unlike a simple resistor, the amplifier presents a low-impedance terminal to the input current. In the SIM918 Precision Current Preamplifier, the electric potential of the input terminal,  $V_{\rm in}$ , is accurately made equal to the user-provided potential at the bias terminal,  $V_{\rm bias}$ , or to ground. The absolute magnitude of the resulting input *offset voltage* is nearly zero:

offset voltage

$$V_{\rm ofs} = V_{\rm in} - V_{\rm bias}, \qquad |V_{\rm ofs}| < 10 \,\mu {\rm V}.$$

virtual ground

In all transimpedance amplifiers, the input potential is kept near that of the bias through the action of negative feedback. When the bias voltage is at ground, the input terminal is often said to present a virtual ground, or a virtual null. Without autozeroing, this virtual ground drifts, in some cases by many millivolts. This error in the electric potential of the input terminal may be unacceptable in precision measurements.

In the SIM918, an autozero circuit measures  $V_{\rm ofs}$  every 2 seconds and makes the adjustment necessary to keep the offset voltage at zero. The autozero feature can be engaged or inhibited remotely or from the front panel, giving the user flexibility in sensitive applications. With autozero inhibited, the preamplifier retains microvolt input accuracy for many hours. When engaged, it takes the autozero only a few cycles of a reference clock to restore the offset to within its specified limits.

The gain, or transimpedance, of the preamplifier can be set to  $R_F = 10^6$ ,  $10^7$ , or  $10^8$  V/A, remotely and from the front panel. Along with voltage accuracy, the SIM918 offers a low input bias current and a current noise that is close to the lower limit imposed by the Johnson noise of the transimpedance.

#### 1.1.2 Clocks

reference clock one pps

The autozero circuit switches between measuring the input offset voltage, and the offset voltage of the zeroing amplifier itself, at one half the frequency of an internal or external *reference clock*. The internal clock signal (typically 1.0 pulse per second, *pps*, i.e. 1.0 Hz) can be selected, remotely or from the front panel, to be output on

<sup>&</sup>lt;sup>1</sup> In the unfortunate but established terminology of electronics, the word *bias* conveys different meanings. The *bias current* is the input current present in the instrument in the absence of a current from an external source.

a rear-panel connector. Alternatively, the same connector can be used to input a clock signal at  $(1.0 \pm 10\%)$  pps (i.e. 1.10 Hz–0.90 Hz), synchronizing the switching to an external source.

The reference clock in the SIM918 operates independently of the oscillator used to clock the digital control circuitry. The latter is designed with a special clock-stopping architecture. The microcontroller is turned on only in the following cases: when the settings are being changed; autozero is turned on or off; and during autocalibration, remote communications, or when an overload condition or an external reference clock event occurs. This guarantees that no digital noise contaminates low-level analog signals.

With autozero off and in the absense of an external clock input, the preamplifier enters a completely quiescent state: no reference clock transitions are present that can disturb the measurement of a low-level electric current.

#### 1.1.3 Cabling and grounding

The SIM918 provides maximum flexibility for cabling and grounding. The input connection can be opened, and the bias voltage can be connected to signal ground.

The shield of the Input BNC can be switched between signal ground, the bias voltage, or the rear-panel Program input (which can be left floating, if desired). With the Program input, a user can supply an excitation potential to an experiment via the shield conductor of the input cable, while the excited current flows through the center conductor to the SIM918. The shield of the Bias BNC can be independently grounded or floated.

The input and bias selections, and those of their shields, can be made via the push of a front-panel button or remotely.

#### 1.1.4 Autocalibration

A user-commanded autocalibration procedure allows one to eliminate the effects of thermal drifts in the autozero circuit, and to reduce output offset voltage.

#### 1.1.5 Remote interface and status

remote interface A remote computer can access the module through the SIM900 Mainframe, using RS-232 or GPIB. All instrument settings can be queried via the remote interface. The SIM918 can be operated outside the SIM900 Mainframe by powering it with its required DC voltages.

1 – 4 Getting Started

If the maximum bias voltage is exceeded, or the chosen gain setting causes the output voltage to exceed its maximum, the appropriate overload LED turns on. If the module cannot lock to an external reference clock signal, an LED indicates an unlocked state. If armed, the module also generates a status signal to alert the user of the overload or unlocked condition.

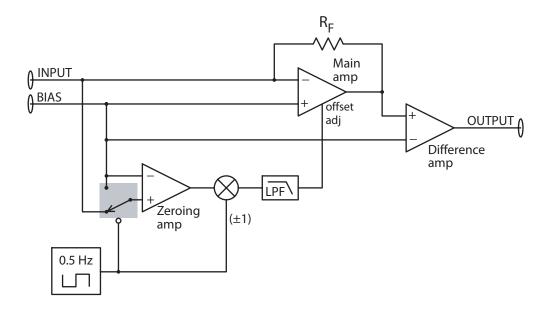

## 1.1.6 Block diagram

The output of the main amplifier (transimpedance stage) is referenced to the bias voltage. A difference amplifier subtracts the bias voltage, so the output of the instrument is directly proportional to the input current  $i_{in}$  and the gain  $R_F$ :

$$V_{\text{out}} = (V_{\text{bias}} - i_{\text{in}} \times R_{\text{F}}) - V_{\text{bias}} = -i_{\text{in}} \times R_{\text{F}}. \tag{1.1}$$

A block diagram of the preamplifier is shown below in Figure 1.1.

Figure 1.1: The SIM918 block diagram.

#### 1.1.7 Front and rear panels

Figure 1.2: The SIM918 front and rear panels.

### 1.2 Front-Panel Operation

#### 1.2.1 Gain

The gain  $R_F$  of the preamplifier, in volts per microampere, is indicated on the front panel of the instrument via a green annunciator LED.<sup>2</sup> Press one of the [GAIN  $\blacktriangleleft \blacksquare$ ] buttons to change the gain. If [GAIN  $\blacktriangleleft$ ] is pressed when  $R_F = 1 \text{ V}/\mu\text{A}$ , the press has no effect. If [GAIN  $\blacksquare$ ] is pressed when  $R_F = 100 \text{ V}/\mu\text{A}$ , the press has no effect.

A simultaneous press of [GAIN  $\rightarrow$ ] has a special meaning. This press initiates autocalibration (Section 2.6).

#### 1.2.2 Autozero

#### 1.2.2.1 Engaging the autozero circuit

The autozero circuit is turned *ON* by the press of a front-panel button. There will be a pause of up to 3.3 seconds (a wait for a positive-going edge of the reference clock). At the end of the pause, the green

<sup>&</sup>lt;sup>2</sup> Note the minus sign in Eq. (1.1); the output voltage is positive for a current that flows *out of* the input terminal.

1 – 6 Getting Started

annunciator LED will turn on and the zeroing circuit will become active.

The same button turns autozeroing off. There will be a less than 1s pause in order for the present control output of the autozero circuit to be sampled and stored. At the end of the pause, the LED indicator will turn off and all switching inside the SIM918 will cease. The sampled control output (trim) will remain applied to the transimpedance-stage amplifier, zeroing it to the best of precision available at the time the autozero circuitry is inhibited.

#### 1.2.2.2 Reference clock detection

The autozero circuit switches at one half the frequency of an internal or external reference clock. If a periodic TTL-level signal is applied to the rear-panel Ref Clock Sync connector, and the connector is not selected for output (see the next section), the preamplifier will recognize the external clock and attempt to lock to the signal. The green *External* LED will illuminate for the duration of the external clock input.

capture range lock acquisition time

If the frequency of the external clock is stable and is between 0.90 Hz and 1.10 Hz, the module will successfully lock to the signal. It typically takes 250 s (just over 4 minutes) to acquire a lock. The yellow *Unlocked* LED is illuminated whenever the SIM918 is not in a locked state. For further discussion of locking, see Chapter 2.5.

For the duration of an unlocked state, the switches in the autozero circuit are not guaranteed to have correct duty cycles. Therefore, the specified input offset accuracy is not guaranteed while *Unlocked*.

The internal reference clock is used when an external clock signal is not present. In this state, neither the *External LED* nor the *Unlocked LED* is illuminated.

#### 1.2.2.3 Output 1 pps sync

The rear-panel Ref Clock Sync connector can be used to output the internal reference clock. The signal at the output is TTL, typically at 1.0 Hz (1.0 pps). The [Output 1 pps sync] button toggles the direction of the signal at the rear-panel connector. The output direction is indicated by a green LED. An inactive *Output 1 pps sync* indicates that the connector may be used to input an external clock.

If [Output 1 pps sync] is pressed while an external reference clock signal is present at the connector, clock output will fail and a Device-Dependent Error (Section 3.5.3) will be issued. If an external signal is applied to the Ref Clock Sync terminal while the connector is selected for output, the external signal will not be recognized.

#### 1.2.3 Input

The [INPUT Open] button opens and closes a relay in the path of the input current. A green LED indicates a disconnected input terminal. The input capacitance of the SIM918 is at its lowest with input open, and is specified in the table on Page viii.

#### 1.2.3.1 Input shield

Successive presses of the [INPUT Shield] button connect the outer shell of the Input BNC to the rear-panel Shield Program Voltage terminal, a buffered copy of the bias voltage, and to signal ground. The state of the input shield connection is indicated by one of three LEDs: the yellow *INPUT Shield Prog*, the yellow *INPUT Shield Bias*, or the green *INPUT Shield GND*.

To float the shield of the Input connector, leave the Shield Program Voltage BNC open and select *INPUT Shield Prog*.

#### 1.2.4 Bias

The [BIAS GND] button toggles the source of the bias between the voltage at the center terminal of the Bias BNC and the signal ground of the instrument. If the bias source is set to ground, the green *BIAS GND* light is on.

With Bias grounded, the difference amplifier (Figure 1.1) is switched out and the output of the instrument is taken directly from the transimpedance stage. With this configuration, there is no common-mode error and the output-offset error is reduced.

When Bias is connected to a user voltage, the voltage is buffered internally before being distributed to other parts of the preamplifier. The offset error of the bias buffer is included in the input offset accuracy specifications in the table on Page viii.

#### 1.2.4.1 Bias overload

bias overload limits

An overload condition is recognized and the *BIAS OVLD* LED is activated if the absolute value of the voltage applied to the Bias input exceeds certain limits. These limits are typically  $\pm 5.0 \, \text{V}$ , and are between

$$-5.2 \text{ V} \le V_{\text{min}} \le -4.9 \text{ V}, \quad 4.9 \text{ V} \le V_{\text{max}} \le 5.2 \text{ V}.$$

The overload LED stays on for a minimum of 50 ms; after this time it turns off if the overload condition has ceased.

1 – 8 Getting Started

#### 1.2.4.2 Bias shield

Successive presses of the [BIAS Shield] button float the outer shell of the Bias BNC and connect it to ground. The state of the bias shield connection is indicated by one of two LEDs: the yellow BIAS Shield Float or the green BIAS Shield GND.

Note that it is the electric *potential* at the Bias terminal, not the potential difference across the Bias connector, that the autozero circuit uses as the reference for the input voltage.

#### 1.2.5 Output overload

output overload limits

An overload condition is recognized and the *OUTPUT OVLD* LED is activated if the absolute value  $|i_{in} \times R_F|$  exceeds certain limits. These limits are typically  $\pm 10.0 \, \text{V}$ , and are between

$$-10.4 \text{ V} \le V_{\text{min}} \le -9.9 \text{ V}, \quad 9.9 \text{ V} \le V_{\text{max}} \le 10.4 \text{ V}.$$

The overloaded state is also recognized, and *OUTPUT OVLD* activated, if the raw output of the transimpedance stage,  $|V_{\rm bias} - i_{\rm in} \times R_{\rm F}|$ , exceeds these limits. To distinguish between the two output overload possibilities, use the OVLD? query. The overload LED stays on for a minimum of 50 ms; after this time it turns off if the overload condition has ceased.

#### 1.3 Connections

There are five BNC connectors in the SIM918, three on the front panel and two at the rear.

| Panel | BNC                    | Terminal | Signal                                                 | Direction     |

|-------|------------------------|----------|--------------------------------------------------------|---------------|

| Front | Input                  | Center   | Input current                                          | Input         |

|       |                        | Shield   | Shield program voltage,<br>bias voltage, signal ground | Output        |

|       | Bias                   | Center   | Bias voltage                                           | Input         |

|       |                        | Shield   | Float, power ground                                    |               |

|       | Output                 | Center   | Output voltage                                         | Output        |

|       |                        | Shield   | Signal ground                                          | Output        |

| Rear  | Shield Program Voltage | Center   | Shield program voltage                                 | Input         |

|       |                        | Shield   | Chassis ground                                         |               |

|       | Ref Clock Sync         | Center   | Reference clock                                        | Input, output |

|       |                        | Shield   | Chassis ground                                         | Input, output |

Table 1.1: BNC connections in the SIM918.

For a further discussion of grounding, see Section 2.2.1. The SIM interface connector is discussed in Section 1.6.1.

1.4 Power-On 1 – 9

#### 1.4 Power-On

The instrument retains the following settings in non-volatile memory:

- 1. The power line frequency (FPLC): 60 Hz or 50 Hz.<sup>3</sup>

- 2. The gain.

- 3. Autozero on/off.

- 4. Input selection (on, open).

- 5. Input shield selection (program, bias, ground.)

- 6. Bias selection (on, ground).

- 7. Bias shield selection (float, ground.)

- 8. Whether or not the phase-locked loop (Section 2.5) stays active when autozero is off.

- 9. Calibration values.

The power-on configuration of the remote interface is detailed in Section 3.3.1.

## 1.5 Restoring the Default Configuration

The default configuration of the SIM918 is:

- 1. Gain 10<sup>6</sup> V/A.

- 2. Autozero on.

- 3. Input connected.

- 4. Input shield at ground.

- 5. Bias at ground.

- 6. Bias shield at ground.

- 7. Reference clock direction is input.

- 8. The phase-locked loop (Section 2.5) is inactive when autozero is off.

To reset the module into this configuration, turn the SIM900 Mainframe power on while holding a front-panel button of the SIM918 for at least 2.0 seconds. The same configuration can also be reached from the remote interface by issuing the \*RST command.

<sup>&</sup>lt;sup>3</sup> FPLC equals the principal rejection frequency of an internal analog-to-digital converter used to measure the input offset trim. See the command OFST.

1 – 10 Getting Started

#### 1.6 SIM Interface

The primary connection to the SIM918 Precision Current Preamplifier is the rear-panel DB–15 SIM interface connector. Typically, the SIM918 is mated to a SIM900 Mainframe via this connection, either through one of the internal mainframe slots or the remote cable interface.

It is also possible to operate the SIM918 directly, without using the SIM900 Mainframe. This section provides details on the interface.

#### 1.6.1 SIM interface connector

The DB–15 SIM interface connector carries all the power and communication lines to the instrument. The connector signals are specified in Table 1.2.

|     |             | Direction              |                                                        |

|-----|-------------|------------------------|--------------------------------------------------------|

| Pin | Signal      | $Src \Rightarrow Dest$ | Description                                            |

| 1   | SIGNAL_GND  | $MF \Rightarrow SIM$   | Signal ground                                          |

| 2   | ¬STATUS     | $SIM \Rightarrow MF$   | Status/service request (GND = asserted, +5 V= idle)    |

| 3   | RTS         | $MF \Rightarrow SIM$   | HW handshake (unused in SIM918)                        |

| 4   | CTS         | $SIM \Rightarrow MF$   | HW handshake (unused in SIM918)                        |

| 5   | ¬REF_10MHZ  | $MF \Rightarrow SIM$   | 10 MHz reference (no connection in SIM918)             |

| 6   | -5V         | $MF \Rightarrow SIM$   | Power supply (no connection in SIM918)                 |

| 7   | -15V        | $MF \Rightarrow SIM$   | Power supply                                           |

| 8   | PS_RTN      | $MF \Rightarrow SIM$   | Power ground                                           |

| 9   | CHASSIS_GND |                        | Chassis ground                                         |

| 10  | TXD         | $MF \Rightarrow SIM$   | Async data (start bit = " $0$ " = +5 V; " $1$ " = GND) |

| 11  | RXD         | $SIM \Rightarrow MF$   | Async data (start bit = " $0$ " = +5 V; " $1$ " = GND) |

| 12  | REF_10MHZ   | $MF \Rightarrow SIM$   | 10 MHz reference (no connection in SIM918)             |

| 13  | +5V         | $MF \Rightarrow SIM$   | Power supply                                           |

| 14  | +15V        | $MF \Rightarrow SIM$   | Power supply                                           |

| 15  | +24V        | $MF \Rightarrow SIM$   | Power supply (no connection in SIM918)                 |

Table 1.2: SIM interface connector pin assignments, DB–15.

#### 1.6.2 Direct interfacing

The SIM918 is intended for operation in the SIM900 Mainframe, but users may wish to directly interface the module to their own systems without the use of additional hardware.

The mating connector needed is a standard DB–15 receptacle, such as Tyco part number 747909–2 (or equivalent). Clean, well-regulated supply voltages of  $\pm 15.0 \,\mathrm{V}$  DC,  $+5.0 \,\mathrm{V}$  DC must be provided, following the pinout specified in Table 1.2 and the minimum currents in the table on Page ix. Ground must be provided on Pins 1 and 8, with chassis ground on Pin 9. The  $\neg$ STATUS signal may be monitored

1.6 SIM Interface 1 – 11

on Pin 2 for a low-going TTL-compatible output indicating a status message. See Section 3.5 for the description of status messages.

The SIM918 has no internal protection against reverse polarity, missing supply, or overvoltage on the +5 V and the  $\pm 15$  V power-supply pins. Supply voltages above 5.5 V on Pin 13, above +16 V on Pin 14, or below -16 V on Pin 7 are likely to damage the instrument. SRS recommends using the SIM918 together with the SIM900 Mainframe for most applications.

#### 1.6.2.1 Direct interface cabling

CAUTION

If the user intends to directly wire the SIM918 independent of the SIM900 Mainframe, communication is usually possible by directly connecting the appropriate interface lines from the SIM918 DB–15 plug to the RS–232 serial port of a personal computer.<sup>4</sup> Connect RXD from the SIM918 directly to RxD on the PC, TXD directly to TxD. In other words, a null-modem-style cable is *not* needed.

To interface directly to the DB–9 male (DTE) RS–232 port typically found on contemporary personal computers, a cable must be made with a female DB–15 socket to mate with the SIM918, and a female DB–9 socket to mate with the PC's serial port. Separate leads from the DB–15 need to go to the power supply, making what is sometimes know as a "hydra" cable. The pin connections are given in Table 1.3.

| DB-15/F to SIM918        |                  | Name                      |

|--------------------------|------------------|---------------------------|

|                          | DB-9/F           |                           |

| 10 ←→                    | . 3              | TxD                       |

| 11 ←→                    | · 2              | RxD                       |

|                          | 5                | Computer Ground           |

|                          | to Power Supply  |                           |

| 7 ←→                     | -15 V DC         |                           |

| 13 ←→                    | +5 V DC          |                           |

| $14 \longleftrightarrow$ | +15 V DC         |                           |

| 1 ←→                     | Signal Ground (s | separate wire to Ground)  |

| 8 ←→                     | Power Ground (s  | separate wire to Ground)  |

| 9 ←→                     | Chassis Ground   | (separate wire to Ground) |

Table 1.3: SIM918 direct interface cable pin assignments.

note about grounds The distinct Signal Ground and Power Ground, and the chassis ground, are *not* directly connected within the SIM918. The power

<sup>&</sup>lt;sup>4</sup> Although the serial interface lines on the DB–15 do not satisfy the minimum voltage levels of the RS–232 standard, these lines are typically compatible with desktop personal computers.

1 – 12 Getting Started

ground carries the return currents of digital control signals, power-intensive analog amplifiers, and the power supplies, whereas the output voltage references to a stable signal ground (Section 2.2.1). When operating in the SIM900, the three grounds are tied together in the SIM900 Mainframe. Signal Ground and Power Ground are connected through back-to-back Schottky diodes, so they cannot be more than  $\sim \pm 0.35\,\mathrm{V}$  apart. The three ground lines should be separately wired to a single, low-impedance ground source at the power supply.

### 1.6.2.2 Serial settings

The initial serial port settings at power-on are: baud rate 9600, 8 bits, no parity, 1 stop bit, and no flow control. The baud rate of the SIM918 cannot be changed. Flow control is not implemented in the SIM918. The parity may be changed with the PARI command.

## 2 Description of Operation

This chapter provides a number of additional details of the operation of the SIM918.

## In This Chapter

| 2.1 | About  | t Transimpedance Amplifiers     | 2-2 |

|-----|--------|---------------------------------|-----|

|     | 2.1.1  | Input capacitance and stability | 2-2 |

|     | 2.1.2  | Choosing the right gain         | 2-3 |

| 2.2 | Bias a | nd Ground                       | 2-4 |

|     | 2.2.1  | Grounds                         | 2-4 |

|     | 2.2.2  | Bias                            | 2-4 |

| 2.3 | Outpu  | ıt                              | 2-5 |

| 2.4 | Autoz  | ero Trim                        | 2-5 |

| 2.5 | Phase- | -Locked Loop                    | 2-6 |

| 2.6 | Autoc  | alibration                      | 2-6 |

| 2.7 | Clock  | Stopping                        | 2-7 |

| 2.8 | Quies  | cent Operation                  | 2-8 |

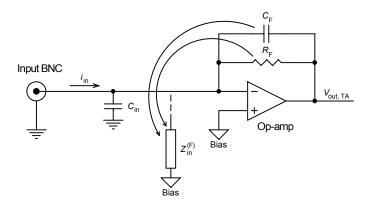

## 2.1 About Transimpedance Amplifiers

transimpedance amplifier

A transimpedance amplifier is an operational amplifier with a resistor in the feedback path. More generally, the feedback impedance  $Z_F$  always has a resistive and a reactive component. The two inputs to the operational amplifier have a very high impedance; and the feedback in the amplifier acts to keep the two inputs at the same electric potential. Therefore, the input current  $i_{\rm in}$  is forced through the feedback impedance, and the amplifier produces an output voltage

$$V_{\text{out, TA}} = V_{\text{bias}} - i_{\text{in}} \times Z_{\text{F}}.$$

The amplifier acts to translate the input current into a proportional output voltage, with the feedback impedance being the coefficient of proportionality. Hence the term *transimpedance*.

The main amplifier of the SIM918 Precision Current Preamplifier is a transimpedance amplifier based on a composite, JFET-input design.

#### 2.1.1 Input capacitance and stability

The input impedance of JFET devices is extremely large. However, the impedance experienced, as a whole, by a current input to the feedback amplifier (i.e. the change in the input voltage<sup>1</sup> divided by the input current) has two other, much more significant contributions in parallel. The first one is the effect of the output on the input via feedback due to finite open-loop voltage gain of the operational amplifier, and the second one is input capacitance.

Figure 2.1: A transimpedance amplifier.

The first term equals the feedback impedance divided by the open-loop gain of the operational amplifier<sup>2</sup>:

$$Z_{\rm in}^{\rm (F)} = Z_{\rm F}/A_{\rm OL}$$

(2.1)

<sup>&</sup>lt;sup>1</sup> Without the action of the autozero circuit.

<sup>&</sup>lt;sup>2</sup> Within the current bandwidth of the transimpedance amplifier.

and is below  $1\,\Omega$  at DC. The open-loop gain is very high at DC, and typically decreases as inverse frequency with a corresponding 90° phase lag:

$$A_{\rm OL} = -j f_{\rm T}/f$$

where  $f_T$  is the gain-bandwidth product of the operational amplifier (~ 10 MHz in the SIM918). Substituting into Equation (2.1), observe

$$Z_{\rm in}^{\rm (F)} = j \, \frac{Z_{\rm F}}{f_{\rm T}} \, f.$$

If the feedback element is purely resistive, the term due to  $Z_{\rm F}$  behaves exactly as if a large inductor were connected between the input and the bias terminals. This contribution to the input impedance increases linearly with frequency, with a corresponding 90° phase lead.<sup>3</sup>

The input terminal always has some amount of parasitic capacitance to the bias terminal, and to ground. The input capacitance specification in the table on Page viii applies for no cable connected to the Input BNC. A coaxial cable adds ~ 100 pF/m of capacitance. Even one meter of coax will dramatically increase the input capacitance.

The input capacitance, in parallel with the effective inductance, can form a resonant tank circuit if the capacitance is large enough that the resulting resonant frequency lies within the bandwidth of the transimpedance amplifier. The SIM918 has adequate compensation (feedback capacitance) to prevent oscillation for up to 100 pF of additional input capacitance.<sup>4</sup> To avoid a feedback oscillation, follow these steps:

- 1. Place the preamplifier as close as possible to the signal being measured, and use the shortest cable length necessary to connect them.

- 2. Reduce all stray capacitance to bias or ground at the output of the experiment under measurement.

- 3. Use a lower gain setting, which reduces the effective input inductance.

Other detrimental effects of excess input capacitance include reduced current bandwidth, poor step response (overshoot and ringing), and increased output noise.

#### 2.1.2 Choosing the right gain

It is important to consider the output resistance (in general, impedance) of the current source being measured. The transimpedance

<sup>&</sup>lt;sup>3</sup> The input voltage leads the input current.

<sup>&</sup>lt;sup>4</sup> Longer cable lengths are tolerated at lower gain settings.

stage amplifies its input voltage noise by the factor<sup>5</sup> of  $(1+R_{\rm F}/R_{\rm source})$ , where  $R_{\rm source}$  is the source resistance. This noise adds in quadrature with the current noise of the stage. To prevent the voltage noise term from dominating the overall output noise, set the current gain to

$R_{\rm F} \lesssim R_{\rm source}$ .

#### 2.2 Bias and Ground

#### 2.2.1 Grounds

The output of the SIM918 is referenced to ground. To maintain the DC accuracy of the instrument, there are two separate ground references. Power Ground (Pin 8 of the SIM interface connector) provides a current return path for digital control signals, power-intensive analog amplifiers, and the power supplies. Signal Ground (Pin 1 of the interface connector) serves as the reference point for analog voltages. The outer shell of the Output BNC connector is tied to Signal Ground. The output current of the preamplifier returns to the power supply through Signal Ground. When *INPUT Shield GND* is selected, the shell of the Input BNC is also tied to Signal Ground.

The outer shells of the rear-panel Shield Program Voltage and Ref Clock Sync BNCs are connected to chassis ground, Pin 9 of the DB–15 SIM interface connector. The separate power, signal, and chassis grounds are *not* directly connected within the preamplifier. When operating in the SIM900 Mainframe, the three grounds are tied together inside the mainframe, and through the mainframe to the Earth. The signal and power grounds are connected inside the SIM918 through back-to-back Schottky diodes, so they cannot be more than  $\sim \pm 0.35 \, \text{V}$  apart.

#### 2.2.2 Bias

The bias potential is received by an ultralow-offset voltage buffer. It is this buffered voltage that appears on the shield of the Input BNC when *INPUT Shield Bias* is selected.

The shield of the Bias connector is not used as a reference for the bias voltage. When Bias Shield GND is selected, the shield is at Signal Ground. The limits on the bias voltage in Section 1.2.4.1 are relative to this ground. A voltage exceeding these limits by more than 1 V will be clamped , through diodes, to  $\pm 5.5$  V relative to Power Ground. The  $10\,\mathrm{M}\Omega$  input resistor is connected between Bias and Signal Ground.

<sup>&</sup>lt;sup>5</sup> At frequencies low enough that the resistive components of the two impedances are dominant.

2.3 Output 2 – 5

To reduce output noise of the SIM918, the Bias input is limited to a bandwidth specified in the table on Page viii. Beyond this frequency, the transimpedance stage cannot follow variations in the bias voltage, but the output difference amplifier (discussed in the next section) does. Hence the common-mode rejection of the instrument is greatly reduced at frequencies above DC.

The bias sensing circuitry is always active, and will signal *BIAS OVLD* when the applied input exceeds the voltage limits in Section 1.2.4.1, even if Bias is set to *GND*.

## 2.3 Output

When Bias is switched to *GND*, the output of the instrument is taken directly from the transimpedance stage; otherwise, from a difference amplifier (Figure 1.1) that subtracts the bias voltage from the output of the transimpedance stage. Both outputs have equal drive capacity.

The output impedance of the SIM918 Precision Current Preamplifier is  $100 \Omega$ . The preamplifier can drive load impedances from  $\infty$  to  $0 \Omega$  for the full  $\pm 10$  V range of output voltage. When driving a  $50 \Omega$  load, the gain will be one third of that displayed on the front panel.

The output signal is filtered by a passive LRC, with  $f_{-3\,dB} = 25\,\text{kHz}$ . The filter eliminates broad-spectrum noise, while adding a negligible amount of overshoot in the step response. The R in the filter contributes to the output resistance.

The output difference amplifier, when engaged (Bias not at [GND]), introduces an offset error that can be greater than the maximum input offset error of the preamplifier. The error is reduced by autocalibration (Section 2.6). The output offset can also be trimmed from the remote interface by using the command OFST 1.

#### 2.4 Autozero Trim

The autozero control loop is fully analog.<sup>6</sup> Its settling time, to within the maximum input offset voltage specification in the table on Page viii, is 40 s. Two adjustments can be made to loop parameters via the remote command OFST. The first one to consider, OFST 3, adjusts the zero point of the loop itself, i.e. the voltage to which the control loop drives the input offset when autozero is *ON*.

The command OFST 2 sets the code in a digital-to-analog converter, the output of which adds together with the output of the loop to form the overall control output of the autozero circuit. When autozero is engaged, the control loop will compensate for changes made

<sup>&</sup>lt;sup>6</sup> With discrete time steps.

via OFST 2, driving the input offset voltage back to a value determined by OFST 3. With autozero off, OFST 3 has no effect and OFST 2 changes the input offset directly.

The best value for OFST 2 is readjusted each time autozero is turned from on to off. If the preamplifier is to be operated under conditions that tolerate absolutely no clock transitions, the recommended course of action is to turn autozero on, let the control loop drive the output to zero and settle, and turn autozero off for the duration of the experiment (Section 2.8).

The value for OFST 3 is reestablished by autocalibration (Section 2.6).

### 2.5 Phase-Locked Loop

The switches in the autozero circuit receive a clock signal from an internal phase-locked loop. If an external reference clock is available at the rear-panel Ref Clock Sync connector, autozero is on, and the connector is not selected for output, the PLL will attempt to lock to the clock signal. The synchronization will be successful for external clock frequencies between 0.90 Hz and 1.10 Hz.

In the internal reference clock mode, the PLL oscillator runs freely, generating a 1.0 Hz square wave with rising edges at the beginning of each autozero half-cycle. The voltage-controlled oscillator in the loop operates at 240 Hz for 60 Hz power line frequency (FPLC), and at 200 Hz for FPLC = 50 Hz.

The PLL can be automatically inhibited, and the voltage-controlled oscillator turned off, when the reference clock is *External* and autozero is off. The behavior is set by the remote command APLL. With APLL OFF, the oscillator turns off. In this mode, under external reference clock, the instrument will undergo the full capture and lock transient after autozero is switched on. To avoid the 4 minute capture delay, set APLL ON. The module restores the last known APLL mode upon power-on.

When autozero is on, the PLL oscillator is always running, regardless of the reference clock source. If the reference clock is internal and autozero is off, the PLL oscillator is off. There is no capture delay under internal clock.

#### 2.6 Autocalibration

To ensure the specified offset accuracy, the preamplifier must be self-calibrated within the 24 hours preceding a measurement. A valid autocalibration must take place at  $(23 \pm 5)$  °C with the module warmed up for at least 2 hours at  $(23 \pm 5)$  °C. If the module is being used inside

the SIM900 Mainframe, the autocalibration must also be inside the mainframe. Otherwise, perform the autocalibration with the same connection to an independent supply as you use for the operation.

Disconnect all inputs and outputs to the SIM918 while performing the autocalibration. Connect the center and shield terminals of the Bias BNC together externally, e.g. with a grounding cap. To calibrate, issue the command ACAL, or press both [GAIN ——] at the same time. Depending on the firmware revision, the calibration may take up to 20 minutes to complete. During the autocalibration, all LEDs are lit. At the end of the calibration, the module returns to its pre-ACAL settings, except the reference clock direction is reset to input.

If autocalibration is unsuccessful, for example because an external current is applied to Input, the calibration constants revert to their original values and the command LDDE? will return Code 2. If an external reference clock is detected, the autocalibration terminates immediately with LDDE? 2.

Autocalibration does not affect gain accuracy.

## 2.7 Clock Stopping

The microprocessor clock of the SIM918 stops if the module is idle, "freezing" the digital circuitry. The following actions "wake up" the clock:

- 1. A power-on.

- 2. A press of a front-panel button.

- 3. Activity (send or receive) at the remote interface.

- 4. An overload.

- 5. A change in external reference clock status: several rising edges at the rear-panel connector while in internal clock mode, or cessation of clocking while in external mode.

- 6. Loss of PLL lock.

The clock runs for as long as is necessary to complete a change of settings requested from the front panel, or to communicate the output of a query through the remote interface. However, the clock will remain active for as long as the overload or unlocked condition exists, and for the full duration of an autocalibration.

This default behavior can be modified with the remote command AWAK. Setting AWAK ON will prevent the clock from stopping. The module returns to AWAK OFF upon power-on.

Note that the operation of the PLL oscillator is completely independent of the microprocessor clock.

## 2.8 Quiescent Operation

Follow these steps to operate the SIM918 Precision Current Preamplifier in sensitive measurements that can tolerate absolutely no module clock transitions:

- 1. Reset the preamplifier (Section 1.5).

- Set Input to Open.

- 3. Wait for at least 40 s.

- 4. Turn autozero off.

- 5. Select the desired gain.

- 6. Close the input.

- 7. Perform the measurement.

After this sequence is complete, the control output of the autozero circuit holds at a value that initially drives the input offset within its specification. Without active autozeroing, the input offset may drift as time progresses, so Steps 1–6 may need to be repeated.

## 3 Remote Operation

This chapter describes operating the SIM918 over the serial interface. \\

## In This Chapter

| 3.1<br>3.2 |        | of Common Commands                         | 3-2 $3-4$ |

|------------|--------|--------------------------------------------|-----------|

| 3.3        |        | luction                                    | 3-6       |

| 3.3        | 3.3.1  | Power-on configuration                     | 3-6       |

|            | 3.3.2  | <u> </u>                                   | 3-6       |

|            |        | Buffers                                    | 3-6 $3-7$ |

| 2.4        | 3.3.3  |                                            |           |

| 3.4        | Comm   |                                            | 3-7       |

|            | 3.4.1  | Command syntax                             | 3-7       |

|            | 3.4.2  | Notation                                   | 3-9       |

|            | 3.4.3  | Examples                                   | 3-9       |

|            | 3.4.4  | General commands                           | 3 - 10    |

|            | 3.4.5  | Configuration commands                     | 3 - 11    |

|            | 3.4.6  | Calibration commands                       | 3 - 14    |

|            | 3.4.7  | Status commands                            | 3-16      |

|            | 3.4.8  | Interface commands                         | 3-19      |

|            | 3.4.9  | Serial communication commands              | 3 - 22    |

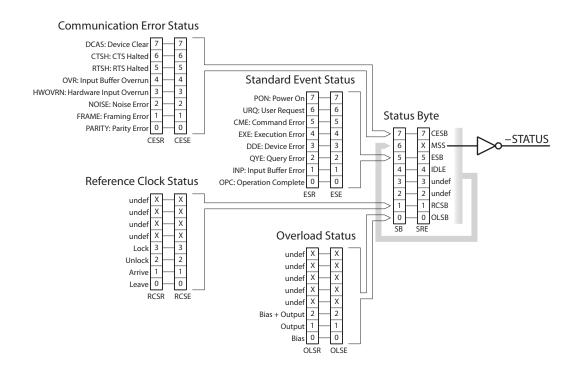

| 3.5        | Status | Model                                      | 3 - 24    |

|            | 3.5.1  | Status Byte (SB)                           | 3 - 25    |

|            | 3.5.2  | Service Request Enable (SRE)               | 3 - 25    |

|            | 3.5.3  | Standard Event Status (ESR)                | 3-26      |

|            | 3.5.4  | Standard Event Status Enable (ESE)         | 3-26      |

|            | 3.5.5  | Communication Error Status (CESR)          | 3-26      |

|            | 3.5.6  | Communication Error Status Enable (CESE) . |           |

|            | 3.5.7  | Overload Status (OLSR)                     |           |

|            | 3.5.8  | Overload Status Enable (OLSE)              |           |

|            | 3.5.9  | Reference Clock Status (RCSR)              |           |

|            | 3.5.10 | Reference Clock Status Enable (RCSE)       |           |

3 – 2 Remote Operation

## 3.1 Index of Common Commands

| Symbol                       | Definition                                                                                                                                                                        |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i<br>j<br>m<br>y, z          | Bit number (0–7) Unsigned integer (0–65535) Unsigned integer (1–3) Literal token                                                                                                  |

| (?)<br>var<br>{var}<br>[var] | Required for queries; illegal for set commands Parameter always required Required parameter for set commands; illegal for queries Optional parameter for both set and query forms |

| General                            |                                          |

|------------------------------------|------------------------------------------|

| HELP(?)                            | 3 – 10 Instrument Help                   |

| AWAK(?) { <i>z</i> }               | 3 – 11 Keep Clock Awake                  |

| Configuration                      |                                          |

| FPLC(?) { <i>j</i> }               | 3 – 12 Power Line Cycle Frequency        |

| GAIN(?) { <i>m</i> }               | 3 – 12 Gain                              |

| INPT(?) { <i>z</i> }               | 3 – 12 Input                             |

| $BIAS(?) \{z\}$                    | 3 – 12 Bias                              |

| $SHLD(?) y \{, z\}$                | 3 – 13 Shield                            |

| CHOP(?) { <i>z</i> }               | 3 – 13 Autozero                          |

| $SYNC(?) \{z\}$                    | 3 – 13 Reference Clock Direction         |

| FREQ?                              | 3 – 13 Reference Clock Frequency         |

| PHAS?                              | 3 – 14 Autozero Phase                    |

| APLL(?) { <i>z</i> }               | 3 – 14 Keep PLL Active                   |

| Calibration                        |                                          |

| ACAL                               | 3 – 14 Autocalibration                   |

| READ? m                            | 3 – 15 Read Microvoltmeter               |

| OFST(?) <i>m</i> {, <i>j</i> }     | 3 – 15 Offset Trim                       |

| Status                             |                                          |

| *CLS                               | 3 – 16 Clear Status                      |

| *STB? [i]                          | 3 – 16 Status Byte                       |

| *SRE(?) [i,] {j}                   | 3 – 16 Service Request Enable            |

| *ESR? [i]                          | 3 – 16 Standard Event Status             |

| *ESE(?) [ <i>i</i> ,] { <i>j</i> } | 3 – 16 Standard Event Status Enable      |

| CESR? [i]                          | 3 – 17 Communication Error Status        |

| CESE(?) [i,] {j}                   | 3 – 17 Communication Error Status Enable |

| OLSR? [i]                          | 3 – 17 Overload Status                   |

| OLSE(?) [i,] {j}                   | 3 – 17 Overload Status Enable            |

|                                    |                                          |

| RCSR? [i]            | 3 – 17 Reference Clock Status        |

|----------------------|--------------------------------------|

| RCSE(?) [i,] {j}     | 3 – 17 Reference Clock Status Enable |

| PSTA(?) { <i>z</i> } | 3 – 18 Pulse ¬STATUS Mode            |

| LBTN?                | 3 – 18 Last Button                   |

| OVLD?                | 3 – 18 Overload                      |

| RCLK?                | 3 – 19 Reference Clock State         |

|                      |                                      |

### Interface

| *RST            | 3 – 19 Reset                |

|-----------------|-----------------------------|

| *IDN?           | 3 – 20 Identify             |

| *TST?           | 3 – 20 Self Test            |

| *OPC(?)         | 3 – 20 Operation Complete   |

| $CONS(?) \{z\}$ | 3 – 20 Console Mode         |

| LEXE?           | 3 – 21 Execution Error      |

| LCME?           | 3 – 21 Command Error        |

| LDDE?           | 3 – 22 Device Error         |

| $TOKN(?) \{z\}$ | 3 – 22 Token Mode           |

| TERM(?) {z}     | 3 – 22 Response Termination |

|                 |                             |

## **Serial Communications**

PARI(?)  $\{z\}$  3 – 23 Parity

3 – 4 Remote Operation

## 3.2 Alphabetic List of Commands

| *                                                        |                                                                     |

|----------------------------------------------------------|---------------------------------------------------------------------|

| *CLS                                                     | 3 – 16 Clear Status                                                 |

| *ESE(?) [ <i>i</i> ,] { <i>j</i> }<br>*ESR? [ <i>i</i> ] | 3 – 16 Standard Event Status Enable<br>3 – 16 Standard Event Status |

| *IDN?                                                    | 3 – 10 Standard Event Status 3 – 20 Identify                        |

| *OPC(?)                                                  | 3 – 20 Operation Complete                                           |

| *RST                                                     | 3 – 19 Reset                                                        |

| *SRE(?) [i,] {j}                                         | 3 – 16 Service Request Enable                                       |

| *STB? [i]                                                | 3 – 16 Status Byte                                                  |

| *TST?                                                    | 3 – 20 Self Test                                                    |

| A                                                        |                                                                     |

| ACAL                                                     | 3 – 14 Autocalibration                                              |

| APLL(?) { <i>z</i> }                                     | 3 – 14 Keep PLL Active                                              |

| $AWAK(?) \{z\}$                                          | 3 – 11 Keep Clock Awake                                             |

| В                                                        |                                                                     |

| BIAS(?) { <i>z</i> }                                     | 3 – 12 Bias                                                         |

| С                                                        |                                                                     |

| CESE(?) [ <i>i</i> ,] { <i>j</i> }                       | 3 – 17 Communication Error Status Enable                            |

| CESR? [i]                                                | 3 – 17 Communication Error Status                                   |

| $CHOP(?) \{z\}$                                          | 3 – 13 Autozero                                                     |

| $CONS(?) \{z\}$                                          | 3 – 20 Console Mode                                                 |

| F                                                        |                                                                     |

| FPLC(?) { <i>j</i> }                                     | 3 – 12 Power Line Cycle Frequency                                   |

| FREQ?                                                    | 3 – 13 Reference Clock Frequency                                    |

| G                                                        |                                                                     |

| GAIN(?) { <i>m</i> }                                     | 3 – 12 Gain                                                         |

| Н                                                        |                                                                     |

| HELP(?)                                                  | 3 – 10 Instrument Help                                              |

| I                                                        |                                                                     |

| INPT(?) {z}                                              | 3 – 12 Input                                                        |

| L                                                        |                                                                     |

| LBTN?                                                    | 3 – 18 Last Button                                                  |

| LCME?                                                    | 3 – 21 Command Error                                                |

|                                                          |                                                                     |

| LDDE?                                                                     | 3 – 22 Device Error                                                                                                                                        |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LEXE?                                                                     | 3 – 21 Execution Error                                                                                                                                     |

| 0                                                                         |                                                                                                                                                            |

| OFST(?) <i>m</i> {, <i>j</i> }                                            | 3 – 15 Offset Trim                                                                                                                                         |

| OLSE(?) $[i,]$ $\{j\}$                                                    | 3 – 17 Overload Status Enable                                                                                                                              |

| OLSR? [i]                                                                 | 3 – 17 Overload Status                                                                                                                                     |

| OVLD?                                                                     | 3-18 Overload                                                                                                                                              |

| P                                                                         |                                                                                                                                                            |

| PARI(?) { <i>z</i> }                                                      | 3 – 23 Parity                                                                                                                                              |

| PHAS?                                                                     | 3 – 14 Autozero Phase                                                                                                                                      |

| PSTA(?) { <i>z</i> }                                                      | 3 – 18 Pulse ¬STATUS Mode                                                                                                                                  |

|                                                                           |                                                                                                                                                            |

| R                                                                         |                                                                                                                                                            |

| RCLK?                                                                     | 3 – 19 Reference Clock State                                                                                                                               |

| RCLK?                                                                     | 3 – 19 Reference Clock State<br>3 – 17 Reference Clock Status Enable                                                                                       |

|                                                                           |                                                                                                                                                            |

| RCLK?<br>RCSE(?) [i,] {j}                                                 | 3 – 17 Reference Clock Status Enable                                                                                                                       |

| RCLK?<br>RCSE(?) [i,] {j}<br>RCSR? [i]                                    | <ul><li>3 – 17 Reference Clock Status Enable</li><li>3 – 17 Reference Clock Status</li></ul>                                                               |

| RCLK?<br>RCSE(?) [i,] {j}<br>RCSR? [i]<br>READ? m                         | <ul> <li>3 – 17 Reference Clock Status Enable</li> <li>3 – 17 Reference Clock Status</li> <li>3 – 15 Read Microvoltmeter</li> </ul>                        |

| RCLK?<br>RCSE(?) [i,] {j}<br>RCSR? [i]<br>READ? m                         | <ul> <li>3 – 17 Reference Clock Status Enable</li> <li>3 – 17 Reference Clock Status</li> <li>3 – 15 Read Microvoltmeter</li> </ul>                        |

| RCLK?<br>RCSE(?) [i,] {j}<br>RCSR? [i]<br>READ? m<br>S<br>SHLD(?) y {, z} | <ul> <li>3 – 17 Reference Clock Status Enable</li> <li>3 – 17 Reference Clock Status</li> <li>3 – 15 Read Microvoltmeter</li> <li>3 – 13 Shield</li> </ul> |

| RCLK? RCSE(?) [i,] {j} RCSR? [i] READ? m  S SHLD(?) y {, z} SYNC(?) {z}   | <ul> <li>3 – 17 Reference Clock Status Enable</li> <li>3 – 17 Reference Clock Status</li> <li>3 – 15 Read Microvoltmeter</li> <li>3 – 13 Shield</li> </ul> |

3 – 6 Remote Operation

#### 3.3 Introduction

Remote operation of the SIM918 is through a simple command language documented in this chapter. Both set and query forms of most commands are supported, allowing the user complete control of the amplifier from a remote computer, either through the SIM900 Mainframe or directly via RS–232 (see Section 1.6.2.1).

See Table 1.2 for the specification of the DB–15 SIM Interface Connector.

## 3.3.1 Power-on configuration

The initial settings for the remote interface are 9600 baud with no parity and no flow control, and with local echo disabled (CONS 0FF).

The following values are retained in non-volatile memory:

- 1. The power line frequency (FPLC).

- 2. The gain.

- 3. Autozero on/off.

- 4. Input selection (on, open).

- 5. Input shield selection (program, bias, ground.)

- 6. Bias selection (on, ground).

- 7. Bias shield selection (float, ground.)

- 8. Whether or not the phase-locked loop stays active when autozero is off.

- 9. Calibration values.

Upon power-on, those settings are restored to their values before the power was turned off.

Where appropriate, the default or power-on value for parameters is listed in **boldface** in the command descriptions.

#### 3.3.2 Buffers

The SIM918 stores incoming bytes from the host interface in a 64-byte input buffer. Characters accumulate in the input buffer until a command terminator (either  $\langle CR \rangle$  or  $\langle LF \rangle$ ) is received, at which point the message is parsed and executed. Query responses from the SIM918 are buffered in a 64-byte output queue.

If the input buffer overflows, then all data in *both* the input buffer and the output queue are discarded, and an error is recorded in the CESR and ESR status registers.

#### 3.3.3 Device Clear